Volume 8. No. 7, July 2020 International Journal of Emerging Trends in Engineering Research Available Online at http://www.warse.org/IJETER/static/pdf/file/ijeter27872020.pdf

https://doi.org/10.30534/ijeter/2020/27872020

# Design and Analysis of Carry Look-Ahead Adder with Reconfigurable Approximation

E. Kiran Kumar, M. Aditya, R. S. Ernest Ravindran\*, A. Sravani, D. Meenakshi, R V Manoj

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India - 522502

# ABSTRACT

In this present research investigation, a productive carry look-ahead adder with a reconfigurable approximation is designed and simulated using mentor graphic tool. This adder has the capacity of changing the states between the rough and careful working modes which helps in making it reasonable for both blunders strong and accurate applications. Approximate circuits permit to exchange off precision and vitality by abusing the natural mistake strength of numerous applications. The structure, which comprises of more area and power productive than best in class reconfigurable inexact adders, is accomplished by certain alterations to the ordinary carry look-ahead adder. The yield of the proposed framework is assessed by utilizing the apparatus called Mentor Graphics, which is the 130 nm technology. The outcomes uncover that the proposed adder gives up to 72% and 65% delay and power decreases contrasted with those of the precise CLA, individually, contrasted with their estimated adders. The proposed structure procedure empowers us to accomplish least power dissipation by streamlining the plan when contrasted with existing systems.

**Key words:** carry look-ahead adder, delay, mentor graphics, power.

# **1. INTRODUCTION**

Power utilization and execution are two significant parameters in the structure of digital devices. The principle testing thing is getting the minimum power and keeping up unwavering quality concerns and getting an ideal execution level. Adders are significant structure obstructs in arithmetic and logic units. Adders, which are used to perform different tasks, for example, subtraction, multiplication and division are the essential parts in processors and are regularly interlinked [1-3].

To meet the power and speed structure limitations, an assortment of strategies at various plan deliberation levels have been proposed. Surmised processing which is a developing model decreases the computational exactness of the outcome for meeting up the base particulars of execution and power effectiveness imperatives for adders [4]. This model is reasonable for the application where the appropriate response isn't a precise set of rough answers are adequate. Surmised arithmetic and logic units are principally funded on the rearrangements of the arithmetic unit circuits [5].

The proposed adder is fully approximate and can be for the most part utilized in mistake strong applications. Correspondingly, there is a consistent degree of deviation from the real outcome. Re-configurability might be considered as a helpful element for any framework that gives different degrees of administration quality during the activity. By lessening the exactness, the power utilization of the unit is decreased just as the propagation delay is diminished bringing abut higher vitality productivity. Furthermore, some advanced frameworks, similar to broadly useful processors, can be utilized for various kinds of figuring like estimated and precise models. What's more, it can switch among correct and rough working modes. This component might be gotten by adding an amendment unit to the surmised circuit that would turn the rough answer for an accurate arrangement [6]. The rectification unit, be that as may, expands the deferral, power, and zone overhead of the structure. Additionally, the mistake revision method may require more than one clock cycle, which could hinder the processing.

Carry look-ahead adder is intended to control the inertness brought about by the gradually expanding influence of the carry bits. The propagation delay which happened in the parallel adders can be disposed of by the carry look-ahead adder [7]. It depends on two things: Calculating each bit position whether that position will engender a carry if another bit rolls in from the right. Combining these determining qualities to have an option to diminish rapidly whether, for every gathering of digits, that gathering will engender a carry that rolls in from the right.

This adder deduces the carry delay by lessening the number of gates through which a carry signal must spread [7,8]. The net impact is that the carries start propagating through every 4-bit group slowly, similarly as in a ripple-carry adder framework, however then moves multiple times quicker, vault over from one look carry ahead adder unit to the following. At last within the digits in that group. Carry lookahead adder comprises of three phases: A propagates block, a sum generator block and carry generator block [1].

A generate block can be written as:

$$G_x = A_x \cdot B_x$$

for, x=0,1,2...

A propagate block can be written as:

$P_x = A_x \bigoplus B_x$  for, x=0,1, 2... A carry output of (x-1)<sub>th</sub> stage is written as:

$$C_{x(cout)} = G_x + P_x C_{x-1}$$

for, x=0,1,2...

A sum output can be written as:

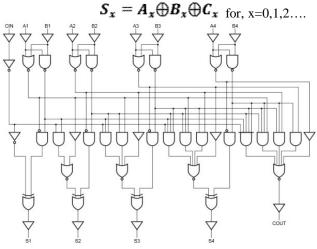

Figure 1: Carry look ahead Adder

In this concise, we represent a reconfigurable inexact carry look-ahead adder (figure 1) which has two working methods of correct and estimated. The structure of the adder, which depends on the regularly carry look forward adder, doesn't require an outer correction unit for the precise include activity.

While the delay and power utilization of the proposed adder, in the definite mode, is about equivalent to those of the ordinary carry look-ahead adder, they are significantly smaller in surmised mode. This is because, in the surmised mode by abusing the power gating method, the power utilization is essentially diminished [9]. Some ongoing related works are checked on and inside the structure of the proposed reconfigurable inexact adder is discussed in various papers.

In nanometer innovation, physical confirmation has gotten a modern, multi-arrange process that requests exceptionally coordinated ways to deal with the preparing and treatment of immense measures of complex structure information. Complete process duration is on the ascent because of progressively minds boggling and bigger plans, higher mistake checks and more confirmation cycles.

#### 2. RELATED WORK

In [1], the carry calculation is done before processing the total which decreases the delay brought about by the carry. The carry select (CS) unit is enhanced by taking out all the repetitive rationale tasks. The carry select adder creates carry words relating to enter carry '0' and '1' which is utilized for rationale improvement of the carry select unit. In [2], to address the plan issues of error compensation unit (ECU) four theorems are created which incorporate assurance of ideal mistake remuneration esteems and recognizable proof of the ideal error pay conspires. What's more, to decrease the

zone and vitality expended, don't cares are proposed to improve the ECU rationale.

In [6], the association of client is decreased which includes the idea of approximating the level by dynamical reconfiguration dependent on the sources of info. The client ought to characterize just the quality required without choosing the guess level. The diminish the time and power. In this, a double mode full adder is proposed which incorporates a multiplexer at the yield to choose the working mode. Because of the utilization of an additional multiplexer in this double mode FA, the delay, area and power utilization are expanded.

In [3], exactness configurable adder is proposed whose precision of results can be arranged to the run time. This adder gives precise outcomes and quality. The power devoured over the procedure is less when contrasted with the traditional adders. In this, the centre of ACA is a surmised adder which comprises of a mistake discovery and error unit. Presently when it is executed, for careful applications it takes a more noteworthy number of cycles for error rectification and recognition. This prompt enormous measure of delay. In [4], OR gates are utilized to lessen the delay and power utilization however it prompts high mistakes. The full adder gates need more space yet basic OR gates require less space which improves the circuit.

In [5], XOR gates are utilized instead of full adders for the least critical part. The most significant some portion of the carry is zero. In any case, the quantity of working modes is restricted to a solitary mode. A reconfigurable rough adder which utilizes a double mode FA has been proposed in [3]. The double mode FA contains the proposed surmised FAs in [1] and an accurate ordinary FA. The yields of the double mode FA are chosen from the yields of these FAs through two multiplexers. Because of utilizing two additional multiplexers for each double mode FA, the delay, area, and per utilization of this methodology in the precise working modes was significantly enormous. In [7], an error decrease unit was acquainted with lessening the mistake of the adder. Be that as it may delay caused due to the ER unit is more contrasted with regular CLA.

In the proposed framework NAND gates are utilized rather than gates. This diminishes the quantity of the transistors required which will decrease the size of the circuit prompting least power dispersal and an upgraded structure. These NAND gates go under the class of general gates. These are noteworthy because any Boolean capacity can be actualized by the utilization of a mix of likewise show the comparative property. This property can be named as utilitarian fulfilment.

# 3. PROPOSED RECONFIGURABLE APPROXIMATE CLA

In the basic CLA, the carry output of the  $x_{th}$  stage is determined from.

$$C_{x+1} = G_x + G_{x-1}P_x + \dots G_0 \prod_{y=1}^x P_y + C_i \prod_{y=0}^x P_y - (1)$$

where Ci is the input carry and Px and  $G_x$  are the propagate  $(A_x \bigoplus B_x)$  and generate  $(A_x B_x)$  signals of the  $x_{th}$  stage, respectively. As increasing the width of the CLA, the delay, area usage and power consumption of the carry generator units increases.

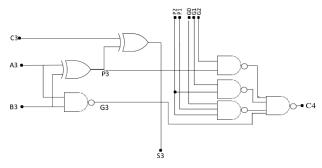

Figure. 2: Gate-level netlist of determining C4 in the proposed RAP-CLA structure.

In brief, we propose to split (1), into two segments. Given a window size of W, the first segment contains W MS terms of (1) while the other segment contains the remaining (LS)terms. Hence, equation (1) may be rewritten as

$$C_{x+1} = \left(\sum_{y=x-W+1}^{x} G_{y}\left(\prod_{k=y+1}^{x-1} P_{k}\right)\right) + \left(\sum_{y=0}^{x-W} G_{y}\left(\prod_{k=y+1}^{x-1} P_{k}\right) + C_{i}\prod_{y=0}^{x} P_{y}\right) - (2)$$

where the left part is called as approximate part and the right part is called a supplementary part. If both of these parts are employed to calculate the carry output, the generated Cx+1 is exact whereas if only the approximate part is used, then generated Cx+1 is imprecise. Hence, (2) may be written as

$$C_{x+1} = \left(\sum_{y=x-W+1}^{x} G_y\left(\prod_{k=y+1}^{x-1} P_k\right)\right) - (3)$$

In this manner, the over (3) is the surmised part which is utilized to produce the Carry yield  $C_{x+1}$  (loosely). Unmistakably figuring uncertain  $C_{x+1}$  is quicker and devours less power contrasted with processing  $C_{x+1}$  unequivocally. Because of this division, two correct and surmised working modes are acknowledged for the proposed reconfigurable inexact adder. Hence, contrasted with the customary CLA, just a single multiplexer can be included the hardware for registering  $C_{x+1}$  in both the working modes. The contributions of this multiplexer are estimated and beneficial carry yields with the working mode signal as the selector.

The working mode signal decides the age of the carry yield in the correct or inexact mode. To expel the power utilization of the beneficial part when the carry age square is in the rough working mode, this part is control gated utilizing pMOS headers. If all the carry generators of a carry depend on the proposed structure, and all the working sign of these units are constrained by just one sign for the working model, all the yield bits of the adder in the estimated mode might be off the base. Where one may build the exactness of the surmised mode by misusing the accurate carry generator for the MS gathering of bits of the carry like the methodology proposed in [3] and [4]. Though, the procedure might be used in structuring CLAs with various degrees of exactness. Like, for structures with flexible precision, the adder ought to be apportioned into certain fragments with their own working mode signals. Truth be told, to look at the adequacy of the proposed structure with those of the past works, the working methods of surmised and careful talked about before are considered.

The NAND gates are utilized to diminish the power and delay as it requires a smaller number of transistors. In any case, in AND gates we require a NAND gate and a NOT gate which will expand the size of the circuit. Additionally, for an OR gate we require a NOT gate pursued by a NAND gate. Presently, on the off chance that we split the AND gates or potentially gates utilizing NAND gates and NOT gates, the cascaded NOT gates will drop each other bringing about a circuit with just NAND gates.

Table 1: Truth Table of the reconfigurable CLA

| A3 | B3 | C3 | P3 | G3 | S3 | C4 |

|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| 0  | 1  | 1  | 1  | 0  | 1  | 0  |

| 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| 1  | 0  | 1  | 1  | 0  | 1  | 0  |

| 1  | 1  | 0  | 0  | 1  | 0  | 1  |

| 1  | 1  | 1  | 0  | 1  | 1  | 1  |

## 4. PERFORMANCE COMPARISON

#### 4.1. Power Dissipation

Power dissipation is a proportion of intensity devoured by the logic gates when they are driven by its information sources. Truth be told, CMOS circuits disperses on static power since there is no immediate way from  $V_{DD}$  to Gnd. There are leakage currents and substrate infusion flows which are prompting static power dissipation in CMOS circuits. One of the principle reasons for intensity scattering is, it emerges from the transient exchanging conduct of CMOS circuits. At one state during the exchanging activity, both NMOS and PMOS are ON and afterwards cut off spot from  $V_{DD}$  and Gnd. Another explanation behind unique control dissipation is charging and releasing of parasitic capacitances which expend the majority of the power used in CMOS circuits. Along these lines, it presumes that CMOS control utilization depends on exchanging exercises of sign utilized.

#### 4.2. Propagation Delay

Propagation Delay is characterized as the time required to arrive at half  $V_{DD}$  of output from the half  $V_{DD}$  of input. The delay is estimated in psec.

E. Kiran Kumar et al., International Journal of Emerging Trends in Engineering Research, 8(7), July 2020, 3045 - 3048

#### **4.3. Power Delay Product**

Power Delay product is the product of average power dissipation to the propagation delay.

| RAP-CLA            | Delay<br>(ps) | Power<br>(µW) | Energy<br>(aJ) |

|--------------------|---------------|---------------|----------------|

| Existing<br>Design | 44.84         | 41.80         | 1874           |

| Proposed<br>System | 38.69         | 35.76         | 1383           |

Table 2: Performance Comparison

The comparison between proposed RAP-CLA and existing design is shown in Table 2. We can observe that in the proposed design there is a decrease in delay and power when compared to an existing design. By using the NAND gates instead of AND gates there will be a decrease in the number of transistors. So, there is a power reduction as the size is optimized. Since the number of transistors is reduced the propagation delay is also minimized when compared to the existing mode.

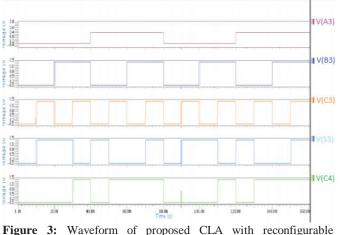

**Figure 3:** Waveform of proposed CLA with reconfigurable approximation.

CLA reconfigurable design(figure 3) was implemented and verified the working of the proposed system in Mentor Graphics tool using 130nm technology. After designing the circuit, it was simulated using the simulator and all design parameters like power, delay from the power analysis were obtained. The propagation delay is reduced as the computation of sum and carry are parallelly done.

## 5. CONCLUSION

High-speed CLA with a reconfigurable approximation is proposed where the adder can change the states between approximate and exact operating modes which can be used for both error-resilient and exact applications. Here much concentration was given towards the approximate mode even though the outcome is inaccurate. All together achieving low power and high-speed circuit. In this research investigation, the logical AND gate was replaced with NAND gates thereby reducing delay and power dissipation. The results showed up to 72 % and 65 % lower delay and power consumption respectively.

# REFERENCES

B. K. Mohanty and S. K. Patel. Area-delay-power efficient carry select adder, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 6 pp. 418–422, Jun. 2014.

https://doi.org/10.1109/TCSII.2014.2319695

- 2. B. Shao and P. Li. Array-based approximate Arithmetic computing: A general model and applications to multiplier and squarer design, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 62, no. 4, pp.1081–1090, 2015.

- M. S. Khairy, A. Khajeh, A. M. Eltawil, and F. J. Kurdahi.. Equi-noise: A statistical model that combines embedded memory failures and channel noise, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 2, pp. 407–419, Feb. 2014.

- H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas. Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010. https://doi.org/10.1109/TCSI.2009.2027626

- 5. N. Zhu, W. L. Goh, W. Zhang, K. S. Yeo, and Z. H. Kong. Design of low-power high-speed truncationerror-tolerant adder and its application in digital

- signal processing, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 8, pp. 1225–1229, Aug. 2010.

- A. B. Kahng and S. Kang. Accuracy-configurable adder for approximate arithmetic designs, in Proc. 49th ACM/EDAC/IEEE Design Autom. Conf. (DAC), San Francisco, CA, USA, 2012, pp. 820–825. https://doi.org/10.1145/2228360.2228509

- J. Hu and W. Qian. A new approximate adder with low relative error and correct sign calculation, in Proc. Design Autom. Test Europe Conf. Exhibit. (DATE), Grenoble, France, 2015, pp. 1449–1454.

- K Mariya Priyadarshini, R. S. Ernest Ravindran. A Novel Two Fold Edge Activated Memory Cell with Low Power Dissipation and High Speed, International Journal of Recent Technology and Engineering (IJRTE). Vol. 8(1), 2019.

- R.S. Ernest Ravindran, Mariya Priyadarshini, Kavuri Mahesh, Vanga Krishna Vamsi, Chaitanya Eswar, Bishan Yasaswi. A Novel 24T Conventional adder vs Low Power Reconstructable Transistor Level Conventional Adder, International Journal of Engineering and Advanced Technology (IJEAT). Vol. 8 (5), 2019.