# 3SSC AND 5VMC BASED DC-DC CONVERTER FOR NON ISOLATED HIGH VOLTAGE GAIN

R.Karuppasamy<sup>1</sup>, M.Devabrinda<sup>2</sup>

1. Student, M.E PED, Easwari engineering college.email:rksamy.3@gmail.com.

2. Assistant Professor of EEE Dept, Easwari engineering college.email:arshhiyadeepak@gmail.com.

Abstract-The high step up dc- dc converter with three state switching cell and five voltage multiplier cells provides continuous input current with reduced ripples and high voltage. The voltage increases by cascading several voltage multiplier cells constituted by diodes and capacitors that operate on the resonance principle. The voltage stress across the elements is reduced due to clamping performed by the output capacitor. Interleaving allows the operation of the multiplier stages with reduction of the current stress through the devices and the size of an input inductors and capacitors is also drastically reduced. It is suitable in cases where dc voltage step-up is demanded, such as electrical fork-lift, audio amplifiers and many other applications.

*Key Terms*—Boost converters, dc–dc converters, high voltage gain, voltage multiplier cells (VMCs).

## I. INTRODUCTION

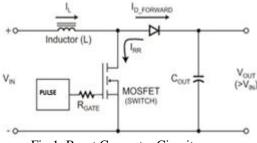

A DC-to-DC converter is a device that accepts a DC input voltage and produces a DC output voltage. Typically the output produced is at a different voltage level than the input. In addition, DC-to-DC converters are used to provide noise isolation, power bus regulation, etc. Boost converter is used when a higher output voltage than input is required.

While the transistor is ON  $V_x = V_{in}$ , and the OFF state the inductor current flows through the diode giving  $V_x = V_0$ . For this analysis it is assumed that the inductor current always remains flowing

(continuous conduction). The voltage across the inductor is shown in Fig.3.1.2 and the average must be zero for the average current to remain in steady state

$$V_{in}t_{on}+(V_{in}-V_o)$$

toff=0 .....(1)

This can be rearranged as

$$V_0 V_{in} = T t_{off} = 1/(1-D)....(2)$$

and for a loss less circuit the power balance ensures

$$I_0/I_{in} = (1-D)....(3)$$

Since the duty ratio "D" is between 0 and 1 the output voltage must always be higher than the input voltage in magnitude. The negative sign indicates a reversal of sense of the output voltage.

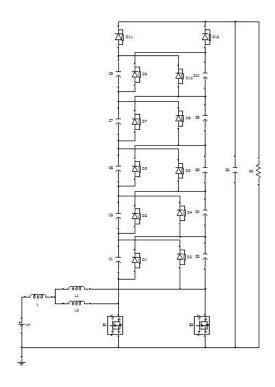

## II. DC-DC CONVERTER WITH VMC

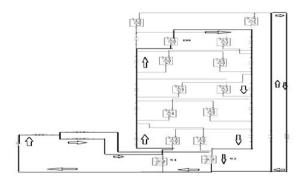

The proposed dc-dc converter has 3ssc and VMC cascaded to produce the high voltage gain. The topology used in the proposed method is that the two boost converters are coupled. So that the current is equally shared between two switches and the voltage doubler characteristics is also achieved. And also interleaving effectively reduces the input output current ripples. Hence the size of the energy storage inductor is reduced. The block diagram of proposed method is shows in fig

#### III. PROPOSED TOPOLOGIES

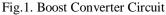

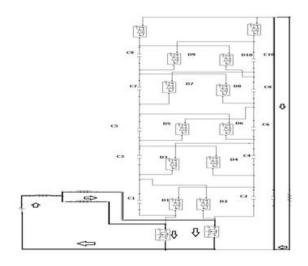

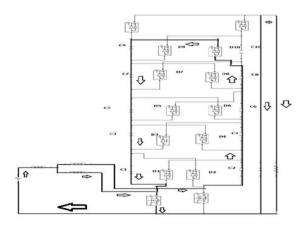

The main circuit diagram of proposed dc-dc converter with 3 state switching cells and voltage multiplier cells is shows in fig.2.

Fig.2.Circuit Of Proposed Converter

In this circuit diagram the switches s1 and s2 are MOSFETs. These Metal oxide semiconductor field effect transistors with reduced on resistance can be used to minimize conduction loss. This proposed topology for voltage step-up applications based on the use of multiplier cells constituted by diodes and capacitors. The converter is able to operate in overlapping mode (when a duty cycle D is higher than 0.5) and non-overlapping mode (duty cycle is lower than 0.5).

## **OPERATING PRINCIPLE**

#### MODE 1

Switches S1 and S2 are turned ON, while all diodes are reverse biased. Energy is stored in

inductor L and there is no energy transfer to the load. The output capacitor provides energy to the load.

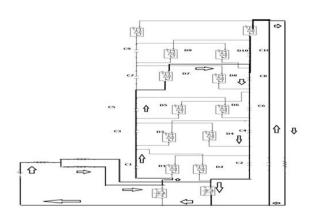

Mode 2

Fig.4.Mode 2

Switch S1 is turned OFF, while S2 is still turned ON and diodeD9 is forward biased. There is no energy transfer to the load as well. Inductor L stores energy, capacitors C1, C3, C5 and C7 are discharged, and capacitors C2, C4, C6, C8 and C10 are charged.

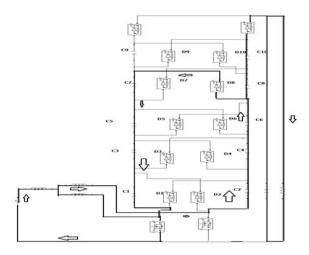

Mode 3

Switch S1 is turned OFF, while S2 is still turned ON and diodeD7 is forward biased, while all

Fig.5.Mode3

the remaining ones are reverse biased. Energy is transferred to the output stage through *D12*. Inductor L stores energy, capacitors C1, C3 and C5 are discharged, and capacitors C2, C4, C6, C8 and C10 are charged.

Mode 4

Switch S1 is turned OFF, while S2 is still turned ON and diodeD5 is forward biased, while all the remaining ones are reverse biased. Energy is transferred to the output stage through *D12*. Inductor L stores energy, capacitors C1 and C3 are discharged, and capacitors C2, C4, C6,C8,C10 are charged.

## Mode 5

Switch S1 is turned OFF, while S2 is still turned ON and diodeD3 is forward biased while all the remaining ones are reverse biased. Energy is transferred to the output stage through *D12*. Inductor L stores energy, capacitor C1 is discharged, and capacitors C2, C4, and C6,C8,C10 are charged.

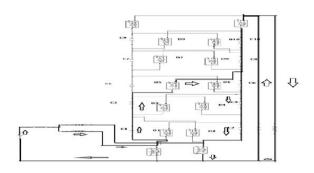

Mode 6

## Fig.8.Mode6

Switch S2 remains turned ON, diode D3 is reverse biased, and diode D1 is forward biased while all the remaining ones are reverse biased. Energy is transferred to the load through D11. The inductor is discharged, and so are capacitors C1, C3, and C5, C7, C9 while C2 is charged.

#### Mode 7

Switch S2 is turned OFF and switch S1 is still turned ON. Diode D10 is forward biased while all the remaining ones are reverse biased. The inductor is charged by the input source, although capacitors C2, C4, C6,C8 are discharged and the capacitors C1, C3,C5, C7,C9 are charged.

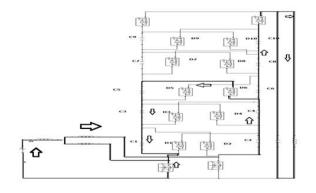

Mode 8

### Fig.10.Mode8

Switches S1 turned ON, DiodeD8 is forward biased, while all the remaining ones are reverse biased. Energy is transferred to the output stage through D12. The inductor stores energy, and capacitors C1, C3, C5, and C7 are charged. Capacitors C2 are discharged, and so are C4, C6, C8, C10.

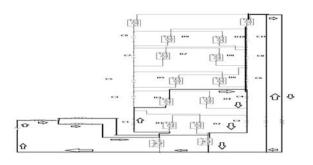

Mode 9

Switches S1turned ON, Diode D6 is forward biased, while all the remaining ones are reverse

biased. Energy is transferred to the output stage through D12. The inductor stores energy, and capacitors C1 and C3, C5, are charged. Capacitors C2 is discharged, and so are C4 and C6, C8, C10. Mode 10

## Fig.12.Mode10

Switches S1turned ON, Diode D4 is forward biased, while all the remaining ones are reverse biased. Energy is transferred to the output stage through D12. The inductor stores energy and capacitors C1and C3 are charged. Capacitors C2 is discharged, and so are C4 and C6, C8, C10.

Mode 11

Switches S1turned ON, Diode D2 is forward biased, while all the remaining ones are reverse biased.

Fig.13.Mode11

Energy is transferred to the output stage through D12. The inductor stores energy, and capacitors C1 is charged. Capacitors C2 is discharged, and so are C4 and C6, C8,C10.

# IV. DESIGN CALCULATION

## INDUCTANCE:

$$\begin{split} L &= (1\text{-}D)^*V^2 \\ D &= T_{\text{ON}}/\text{TOTAL TIME} \\ &= 20/40 \text{ E}^{-6} \\ D &= 0.5\text{e}^{-6} \\ &= (1\text{-}0.5\text{e}^{-6})^*(54)^2 \\ &= 0.5^*10^{-6}*2916 \\ L &= 1500\text{e}^{-6}\text{H} \\ L_1 &= L/2 \\ L_1 &= 750\text{e}^{-6}\text{H} \\ L_1 &= L_2 \\ L_2 &= 750\text{e}^{-6}\text{H} \\ \end{split}$$

Where D = duty ratio V = initial voltage

## FILTER CAPACITANCE:

$$\begin{split} C_{\rm O} &= (1\text{-}D) * V_{\rm in} * T_{\rm on} \\ &= (1\text{-}0.5) * 54 * 20 e^{.6} \\ C_{\rm O} &= 270 e^{.6} F \\ \text{Where } T_{\rm on} &= \text{ON Time} \end{split}$$

## FILTER RESISTOR:

$$2f_c = R/2*3.14*L_1^2$$

2\*0.00004 = R/2\*3.14\*750\*750

R =~3000hms

# VOLTAGE DIVIDING CAPACITOR:

$$C = 2V_{in}$$

=2\*54

=108

We using 10 capacitor, so divide by 10

= 108/10

C = 10UF

## V. SIMULATION RESULTS

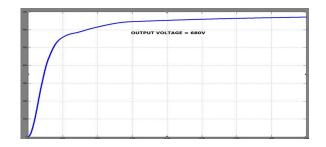

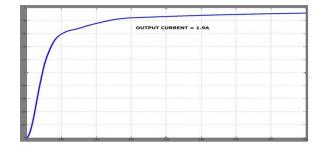

An experimental prototype for the structure with five multiplier cells has been designed and implemented with MATLAB-SIMULINK software.

Fig.14.Output Voltage

## Fig.15.Output Current

# VI. CONCLUSION

This project has proposed non isolated high voltage gain DC-DC converters. To verify the principle operation of the generated structures, the boost converter was chosen. The topology is adequate for several applications such as photovoltaic systems, fuel cell systems and UPS, where high voltage gain between the input and output voltage is demanded. An important characteristic that can be seen in the experimental results is the reduced blocking voltage across the controlled switches compared to similar circuits, allowing the utilization of MOSFETs with reduced on resistance. Besides, the advantages of the 3SSC are also incorporated into the resulting topology, Furthermore only part of the energy from the input source flows through the active switches, while the remaining part is directly transferred to the load through passive components, such as the diodes. The qualitative analysis, analysis, losses modeling, theoretical and experimental results for the converter achieves about 95.3% efficiency at rated load.

# REFERENCES

- 1. S.V.Araujo, R.P.Torrico-Bascope, G.V. Torrico-Bascope, and L. Menezes, "Stepup converter with high voltage gain employing three state switching cell and voltage multiplier," in *Proc. Power Electron. Spec. Conf.*, 2008, pp. 2271–2277.

- R.A. Da Camara, C. M. T. Cruz, and R.P. Torrico-Bascope, "Boost based on threestate switching cell for UPS applications," in *Proc. Brazilian Power Electron. Conf.*, 2009, pp. 313–318.

- K. C. Tseng and T. J. Liang, "Novel highefficiency step-up converter," *IEE Proc.– Electr. Power Appl.*, vol. 151, no. 2, pp. 182–190, Mar. 2004.

- M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage multiplier cells applied to non-isolated converters," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 871–887, Mar. 2008.

- Y. R. Novaes, A. Rufer, and I. Barbi, "A new quadratic, three-level, dc/dc converter suitable for fuel cell applications," in Proc. Power Convers.Conf., Nagoya, Japan, 2007, pp. 601–607.

- 6. K. C. Tseng and T. J. Liang, "Novel highefficiency step-up converter," IEEE Proc. – Electr. Power Appl., vol. 151, no. 2, pp. 182–190, Mar. 2004

- 7. O.Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Boost converter with high

voltage gain using a switched capacitor circuit," in Proc. Int. Symp. Circuits Syst., 2003, pp. III-296–III-299.

- X.G. Feng, J. J. Liu, and F. C. Lee, "Impedance specifications for stable dc distributed power systems," IEEE Trans. Power Electron., vol. 17, no. 2, pp. 157–162, Mar. 2002.

- Y. R. Novaes, A. Rufer, and I. Barbi, "A new quadratic, three-level, dc/dc converter suitable for fuel cell applications," in Proc. Power Convers. Conf., Nagoya, Japan, 2007, pp. 601–607.

- C. T. Choi, C. K. Li, and S. K. Kok, "Modeling of an active clamp discontinuous conduction mode flyback converter under variation of operating condition," in Proc. IEEE Int. Conf. Power Electron. Drive Syst., 1999, pp. 730–733.

- K. C. Tseng and T. J. Liang, "Novel highefficiency step-up converter," IEE Proc.– Electr. Power Appl., vol. 151, no. 2, pp. 182–190, Mar. 2004.

- O. Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Boost converter with high voltage gain using a switched capacitor circuit," in Proc. Int. Symp. Circuits Syst., 2003, pp. III-296–III-299.

- Y. Jang and M. M. Jovanovic, "Interleaved boost converter with intrinsic voltagedoubler characteristic for universal-line PFC front end," IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1394–1401, Jul. 2007.

- J. Yungtaek and M. M. Jovanovic, "New two-inductor boost converter with auxiliary transformer," IEEE Trans. Power Electron., vol. 19, no. 1, pp. 169–175, Jan. 2004.

- R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved boost dc–dc converter with large conversion ratio," in Proc. IEEE Int. Symp. Ind. Electron., 2003, pp. 411–416.

- M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage multiplier cells applied to non-isolated converters," IEEE Trans. Power Electron., vol. 23, no. 2, pp. 871–887, Mar. 2008.