Volume 9, No.3, May - June 2020

International Journal of Advanced Trends in Computer Science and Engineering

Available Online at http://www.warse.org/IJATCSE/static/pdf/file/ijatcse201932020.pdf https://doi.org/10.30534/ijatcse/2020/201932020

R. S. Ernest Ravindran\*, Chella Santhosh, S. Surya Teja, S. Arun Sujash, M. Vijay, K. Umesh

<sup>1</sup> Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation,

Vaddeswaram, AP, India - 522502

# ABSTRACT

The advancement in technology increases day by day, that the conventional based CMOS VLSI technology reached its peak due to physical limits like power dissipation and size. In order to overcome this, a new alternative method has introduced to recurrently improve the development of digital electronics. Quantum-Dot Cellular Automata (QCA) approach is nanotechnology which is an emerging technology provides an efficient platform to overcome the confines of existing CMOS. In this research investigation a novel design of 4-bit reversible and non-reversible binary to gray (B-G) and gray to binary code (G-B) converter was simulated with the help of QCA tool and the obtained results were found to be efficiently better when compared with that of the previous one.

**Key words:** Quantum-dot Cellular Automata (QCA), CMOS, Binary to gray Code Converter, Gray to binary converters.

## **1. INTRODUCTION**

Innovation advancement and modern industrial competition have been driving the semiconductor business to make smaller, faster and less power consumption powerful devices. By the emphasis of miniaturization, the modern semi-conductor technology is characterized. Traditionally the microelectronics is scaled down to Nano electronics, this future system that comprise of these nanometric structures require both novel modern switching devices and architectures. Quantum-Dot Cellular Automata (QCA), an embryonic invention proposed by Craig S. Lent et al in 1993 [1]. He focused on the idea of employing cellular Architectures which are companionable with Quantum Devices. The QCA allows to operate in THz frequency range with larger the device integration density more than that of CMOS [2-4]. In the CMOS VLSI circuits, the data transfer by the means of electric current between the transistors, whereas in QCA the binary information (0s and 1s) is projected in the form of charge configuration in the cell of QCA [5-7]. The most efficient cell reduction techniques are implemented on code converters.

The essential unit in QCA is cell which is formed by four Quantum-Dots placed at the four corners of a square [8-10]. Quantum dots are nano-based material with zero dimension, synthesised from usual semiconducting materials like InAs/GaAs. The cell also consists of two electrons which occupy the diagonal due to coulomb electro-static repulsion. In the cell the position of electrons is denoted by the polarization P (P = +1 and P = - 1).

The linear arrangement of QCA cells patterns a binary wire the information is transferred along the wire by the Columbic interaction between the adjacent OCA cells. For electrostatic communication, the input cell is strongly polarized in one direction and the signal propagates from one end to another. The essential power required to run the circuit and to control information flow in QCA circuits is carried out by clock [11]. Here the clock involves of 4 phase such as Hold, Relax, Release, and Switch. The QCA circuit is divided into clock zones and the cells in the zone are controlled using the signal. There is 900 phase lag between each clock. To govern the polarization effects and reactions, one should hold the polarization of the first cell fixed and lower the potential barrier of its neighbouring cell to let the electrons of the adjacent cell to displace. To perform phenomenon should repeat repeatedly to pass the information through cells these clock zones are necessary.

The intersection of two QCA wires is known as QCA crossover. There are two types of cross overs mostly used in QCA those are Multi-layer approach and co-planar approach. In Multi-layer approach, data is transferred through another layer over the main layer whereas, in Coplanar approach, by rotating the QCA-cells at 450 vertical wire can be achieved [12-15].

Code converters are circuits that convert code into another which is programmed in logic arrays and used in many fields such as protecting information from third parties and increase data flexibility. It is also efficient in the security department for devising and cracking codes. These reversible code converters can show the results of converted binary code as well as given input binary code such that this system performs a crucial role in the field [16-20].

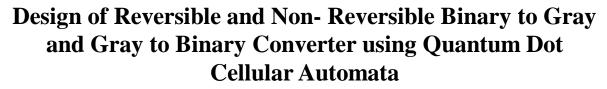

Figure 1: 4-bit B to G code converter schematic

### 1.1. Binary to Gray (B-G) converter

Binary code is the simplest form of computer code which consist of a sequence of bits either '0' or '1' [16-18]. Let's assume four digits B3, B2, B1, and B0 are taken as a binary number and G3, G2, G1, and G0 be gray code (Figure. 1), the logic expression of the B to G code conversion is expressed as, G3 = B3;  $G2 = B3 \oplus B2$ ;  $G1 = B2 \oplus B1$ ;  $G0 = B1 \oplus B0$ ;

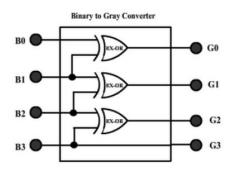

Figure. 2: 4-bit G to B converter schematic.

#### 1.2 Gray to Binary converter

Gray code is known as reflective code [19, 20]. In Gray code successive code bits vary in a one-bit position that's why it is popular for unit distance code, and G to B code conversion (Figure. 2) expression written as,

B3 = G3; B2 = B3 ⊕ G2; B1 = B2 ⊕ G1; B0 = B1 ⊕ G0; Whereas, ⊕ represents the Ex-OR operation between the digits.

# 2. PROPOSED METHOD 2.1. Feynman Gate

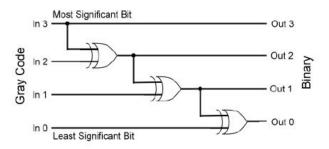

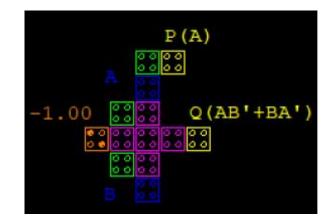

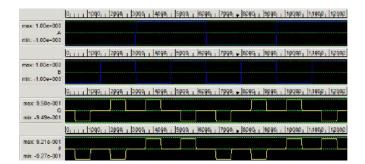

Feynman gate (FG) is known as CNOT gate which consist of 2 x 2 reversible gate, where A and B inputs are plotted to P and Q outputs, P = A and  $Q = (A \oplus B)$  Figure 3. shows the logic schematic of Feynman Gate. FG is designed to use it for designing Reversible code converters Figure 4 represents the proposed layout of Feynman gate, whereas the waveform of Feynman is shown in Figure 5.

Figure 3: Schematic layout of the Feynman Gate

Figure 4: Proposed Feynman Gate QCA simulation

Figure 5: Feynman gate output waveforms

# **2.2.** Non-reversible 4-bit binary to gray and gray to binary code converters

The proposed layouts 4-bit binary to gray code converter consist of 33 cells with area of  $0.04 \ \mu m^2$  and the non-reversible gray to binary code consisting of 39 cells with area  $0.06 \ \mu m^2$  the cell count is reduced in this layout and 2 crossovers are used between the cells as shown in Figure 6 and 7 [16-18]. Figure 8 and 9 show the waveform of the non-reversible 4-bit B to G and G to B code converters. The obtained results were equated with that of the existing approaches and found to be efficient as tabulated in Table 1&2.

Figure 6: QCA layout of 4-bit B to G

| _   | _  | _   | _   |     |    |    |      | _   | _   | _  |      |     | _    | _   | _   | _  | _   | _   | _   | _    | _    |      | _    | _     |      |            |     | _   |     |    |    | _   |     |     |     |     |     | _   | _  |   | _ | _ | _   |   |

|-----|----|-----|-----|-----|----|----|------|-----|-----|----|------|-----|------|-----|-----|----|-----|-----|-----|------|------|------|------|-------|------|------------|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|----|---|---|---|-----|---|

|     |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

| • • |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       | ٠.   |            |     |     |     |    |    |     |     |     |     |     | ۰.  | -   |    |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       | •    | в.         | 4   |     |     |    |    |     |     |     |     |     | •   | Β.  | 3  |   |   |   |     |   |

| • • |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       | 10   |            | 1   |     |     |    |    |     |     |     | 'n  |     | 1 C |     | T. |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     |      | З.  |     |    |     |     |     |      |      |      |      |       | 2    | 0.0        |     |     |     |    |    |     |     |     | 15  | 12  | H.  | 1   | 1  |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       | 16   | Ļο         | 1   |     |     |    |    |     |     |     | 19  | ÷   | 16  | 10  | Ц. |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     |      | 0.0 | L   |    |     |     |     |      |      |      | K    | 2,0   | 4    | <u>,</u> a | 1   | 0.0 | L   |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     |     |    |      |     | 2    | 0.0 | ι.  |    |     |     |     |      |      |      | Ľ    | c < c | 4    | 0.0        | 4   | 00  |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    | R   | n   |     |    |    |      |     |     |    | r    | 0.0 | Te   | 0.0 | llo | î0 | T - |     |     |      |      |      | Г    | 0     | 1.   |            | 1   |     | - 4 | ño | 18 | οē  | 16  | Э¢  | 16  | 0.0 |     | ÷с  | П  |   |   |   | 0   |   |

|     |    | D   | Ψ,  |     |    |    |      |     |     |    | 10   | 0.0 | Ĭ¢.  | 00  | ĬC  | 0  | 1   |     |     |      |      |      | 1    | Ä     | 1    |            |     | - 1 | -14 | ٢a | I< | 20  | 10  | ) a | 1   | 50  | k   | 0.6 |    | - | 1 |   | U   | 0 |

| • • | T  | a'ı | ali | 0 0 | T, |    |      |     |     |    | 5    | 5   | 1    |     |     | 1  | Ìc  | i c | nie | o e  | 1 L  | o te | जार  | ÷.    |      | i n        | i i |     |     |    | 1z | i Z | n'  |     | 1   | 2   | 1   |     |    |   |   |   |     |   |

|     | 1  | 2.0 | ol. | 5'0 | Ł  |    |      |     |     |    | 1.   | х   | Ł    |     |     |    | 10  | a.  | ьHа | 1    | s th | 5.6  | s He | 12    | 1e   |            | ł.  |     |     |    | 12 | 12  | ıt. |     |     |     |     |     |    |   |   |   |     |   |

| • • | 1  |     |     |     | 72 | 10 | ÎГ.Я | 10  | лb  | 10 | a É  | 2.0 |      | 10  |     |    | Ľ   |     | ٠,  | 3    | ÷    |      | 2    |       | -11- |            | •   |     |     |    | 17 | 1   |     |     |     |     |     |     |    |   |   |   |     |   |

| • • |    |     |     |     | Ð  | 88 | H)   | 65  | Ю   | 8  | CIC) | 22  | HZ   | 1   |     |    |     |     | -12 | 8    | ÷.   |      |      |       |      |            |     |     |     |    |    | 12  | ÷   |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     | j, |    | 1Ľ   | Ŧ   | ųr. | ÷  | цĽ   | ÷   | 1)22 | -   | ι,  |    |     |     | -44 | 1    | Ц.   |      |      |       |      |            |     |     |     |    | 1  | -   | Ц., |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    | 19   | .0  | 1   |    |      |     |      |     | 1   |    | 0   | à   | 1   | 2.5  | 1    |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    | Ľ    | 0.0 | 1   |    |      |     |      |     | ÷   |    | Υ.  | Ŷ   | L   | 3 (C | Ч,   |      |      |       |      |            |     |     |     |    |    | .1  |     |     | ).( | ).  |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    | ¢    |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    | 1    | 0   | 1   |    |      |     |      |     |     |    |     |     | 1   |      | 0    | 0    |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    | 1    |     |     |    |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     |    |     |     |     |    |    |      |     | ò   | Ó  |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

| • • |    |     |     |     |    |    | 1    |     | U   | U  |      |     |      |     |     |    |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   |     |   |

|     | ٠. |     |     |     |    |    |      |     |     |    |      |     |      |     |     | •  |     |     |     |      |      |      |      |       |      |            |     |     |     |    |    |     |     |     |     |     |     |     |    |   |   |   | 1.0 |   |

Figure 7: 4-bit G to B code converter

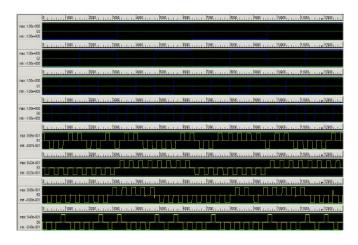

Figure 8: 4-input B to G code converter wave form

Figure 9: Waveform for 4-bit G to B code converters

Table 1: Non-reversible converter comparison table for B-G

|                     | 4-bit B to G code converter |               |      |      |  |  |  |  |  |  |

|---------------------|-----------------------------|---------------|------|------|--|--|--|--|--|--|

| Parameters          | <b>D</b>                    | Previous Work |      |      |  |  |  |  |  |  |

|                     | Proposed                    | [16]          | [17] | [18] |  |  |  |  |  |  |

| Cells               | 33                          | 37            | 127  | 192  |  |  |  |  |  |  |

| Area (μ <b>m²</b> ) | 0.04                        | 0.04          | 0.41 | 0.34 |  |  |  |  |  |  |

| Crossover           | 0                           | 0             | 3    | 3    |  |  |  |  |  |  |

| Latency             | 0.5                         | 0.95          | 0.75 | 2    |  |  |  |  |  |  |

Table 2: Non-reversible converter comparison table for G-B

| Parameters          | 4-bit G to B code converter |               |      |      |  |  |  |  |  |  |

|---------------------|-----------------------------|---------------|------|------|--|--|--|--|--|--|

|                     | Proposed                    | Previous Work |      |      |  |  |  |  |  |  |

|                     | 1.010000                    | [16]          | [17] | [18] |  |  |  |  |  |  |

| Cells               | 39                          | 47            | 99   | 269  |  |  |  |  |  |  |

| Area (μ <b>m²</b> ) | 0.06                        | 0.05          | -    | 0.69 |  |  |  |  |  |  |

| Crossover           | 2                           | 0             | 0    | 0    |  |  |  |  |  |  |

| Latency             | 0.75                        | 1             | 0.75 | 6    |  |  |  |  |  |  |

# 2.3. 4-bit Reversible B to G and G to B code converter

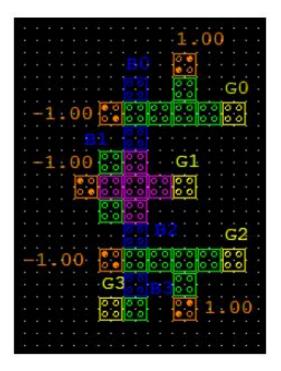

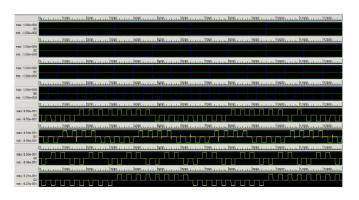

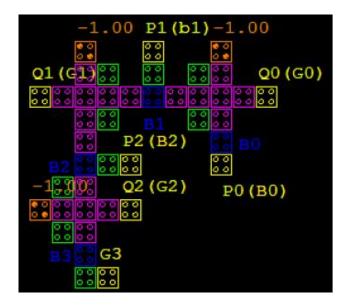

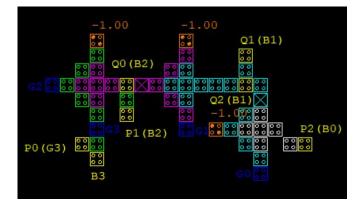

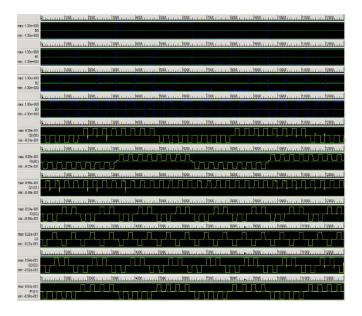

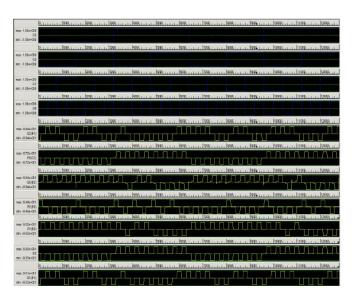

A novel layout for reversible 4-bit B to G and G to B code converters using Feynman gate is proposed. Table 3 & 4 shows the simulation factors of the proposed layout with previous work [19, 20]. Figure 10 & 11 shows the layout of 4-bit reversible B to G and G to B. The count of QCA cells and area of the proposed layouts has been reduced and the performance was found to be improved when compared with that of the previous work, the waveforms of 4-bit reversible B to G and G to B was shown in Figure 12 & 13.

Figure 10: QCA layout of reversible binary to gray.

Figure 11: QCA layout four 4 -bit reversible Gray to Binary converter.

Figure 12: Waveform of 4-bit reversible binary to gray code converter.

Figure 13: Waveform of 4-bit reversible gray to binary code converter.

## **3. RESULTS AND DISCUSSION**

The layouts of all circuits have been designed in QCA designer 2.0.3. The parameters are used for bistable Approximation, 12800 Number of samples, 65.000000nm radius of effect, 0.001000 convergence tolerance, 11.500000 layer separation, 12.900000 relative permittivity, 9.800000e<sup>-22</sup> J clock high, 3.800000e<sup>-023</sup> J clock low, 0 clock shift, 2.000000 clock amplitude factor and 100 maximum iterations per sample. The tabular forms show the comparative analysis of proposed models with existing models this paper mainly focused on reducing cell count which further reduces the cell area, that was successfully achieved by proposed layouts and the following Table 3 & 4

forms describes the comparative analysis of the proposed work with that of the previous work.

|                     | 4-bit B to G code converter |               |      |  |  |  |  |  |  |

|---------------------|-----------------------------|---------------|------|--|--|--|--|--|--|

| Parameters          |                             | Previous Work |      |  |  |  |  |  |  |

|                     | Proposed                    | [19]          | [20] |  |  |  |  |  |  |

| Cells               | 49                          | 108           | 118  |  |  |  |  |  |  |

| Area (μ <b>m²</b> ) | 0.06                        | 0.11          | 0.38 |  |  |  |  |  |  |

| Crossover           | 0                           | 1             | 2    |  |  |  |  |  |  |

| Latency             | 0.75                        | 0.75          | 0.75 |  |  |  |  |  |  |

Table 3: 4-bit reversible converter for B-G

| Parameters             | 4-bit G to B code converter |               |      |  |  |  |  |  |  |

|------------------------|-----------------------------|---------------|------|--|--|--|--|--|--|

|                        | Proposed                    | Previous Work |      |  |  |  |  |  |  |

|                        |                             | [19]          | [20] |  |  |  |  |  |  |

| Cells                  | 52                          | 77            | 112  |  |  |  |  |  |  |

| Area<br>(μ <b>m²</b> ) | 0.010                       | 0.1           | 0.36 |  |  |  |  |  |  |

| Crossover              | 2                           | 1             | 2    |  |  |  |  |  |  |

| Latency                | 0.75                        | 0.75          | 1    |  |  |  |  |  |  |

## 4. CONCLUSION

The paper is about designing 4-bit B to G code and G to B reversible and non-reversible B to G and G to B code converters using Quantum-Dot cellular Automata, adapting majority gate techniques. By employing Feynman gate the QCA cell count is reduced thereby the area was reduced. The proposed layouts are shown good expected results and comparative analysis is also done with best existing models.

# REFERENCES

[1] C.S. Lent, P.D. Tougaw, W. Porod, and G.H. Bernstein, Quantum cellular automata, Nanotechnology, vol. 4, pp. 49– 57, 1993.

https://doi.org/10.1088/0957-4484/4/1/004

[2] G Surya Kranth, R. S. Ernest Ravindran, Design and Implementation of Content Addressable Memory Unit using Qunatum Dot, International Journal of Recent Technology and Engineering, Vol.8(4), 2019.

https://doi.org/10.35940/ijrte.D4706.118419

[3] Chella Santhosh, R. S. Ernest Ravindran, Uday Bhanu Prakash Vulchi, Venkatesh Thumati, Mohammad Shifathul Gufran, D. Bhavana, Sree Vardhan Cheerla, Design and Verification of Half Adder using Look Up Table (LUT) in Quantum Dot Cellular Automata (QCA), International Journal of Advanced Science and Technology, Vol. 28, No. 16, (2019), pp. 1804 – 1809.

[4] R. S. Ernest Ravindran, K Mariya Priyadarshini, Dangeti Peda Manikya Pavana Teja, Popuri Nikhil Chakravarthy, Peruboyina Dharma Teja, Design of RAM using Quantum Cellular Automata (QCA) Designer, International Journal of Scientific & Technology Research, Vol.8(08), 2019, 1385-1391.

[5] Naveen Sai D., Surya Kranth G., Paradhasaradhi D., Ernest Ravindran R.S., Lakshmana Kumar M., Mariya Priyadarshini K. (2019) Five Input Multilayer Full Adder by QCA Designer. In: Singh M., Gupta P., Tyagi V., Flusser J., Ören T., Kashyap R. (eds) Advances in Computing and Data Sciences. ICACDS 2019. Communications in Computer and Information Science, vol 1046. Springer, Singapore.

https://doi.org/10.1007/978-981-13-9942-8\_16

[6] G Surya Kranth, D Naveen Sai, R. S. Ernest Ravindran, Study and Analysis of 3 -Input Logic Gates by Using Quantum Dot Cellular Automata, International Journal of Recent Technology and Engineering, Vol.7(6), 2019, 1270-1274.

[7] J. Lakshmi Prasanna, R.S. Ernest Ravindran, M. Ravi Kumar, K. Sree Pooja, U V S Sumanth, Shaik Ahamed and Chella Santhosh, Design of BCD Adder using Quantum Cellular Automata, International Journal of Advanced Trends in Computer Science and Engineering, Vol. 9(1), 2020, 574-578.

https://doi.org/10.30534/ijatcse/2020/79912020

[8] Seminario J.M, Derosa P.A, Cordova L.E and Bozard B.H., A molecular device operating at terahertz frequencies, IEEE Transactions on Nanotechnology, 3(1), 2004, 215–218.

[9] Lent C. S. and Tougaw P. D, Lines of interacting quantum dot cells: a binary wire, Journal of Applied Physics, vol. 74, pp: 6227-33, 1993.

[10] Zhang, R., Walus, K., Wang, W., and Jullien, G. A., A method of majority logic reduction for Quantum cellular automata, IEEE Transactions on Nanotechnology, 3(4), 2008, 443-450.

https://doi.org/10.1109/TNANO.2004.834177

[11] Kevin Hennessy and Craig S. Lent, Clocking of molecular quantum-dot cellular automata, J. Vac. Sci. Technol. B 19.5., Sep-Oct 2001

[12] P. D. Tougaw and C. S. Lent, "Logical devices implemented using quantum cellular automata", Journal of Applied Physics, vol. 75, iss. 3, pp. 1818-1825, February 1, 1994.

[13] Bandan Bhoi1, Neeraj Kumar Misra and Manoranjan Pradhan, Design and evaluation of an efficient parity-preserving reversible QCA gate with online testability, Bhoi et al., Cogent Engineering (2017), 4: 1416888.

[14] P. Chaithanya, B. Ramesh, V. Srujana, V. Vikram, Implementation of Efficient Binary To Gray Code Converter Using Quantum Dot Cellular Automata, International Journal for Research in Applied Science & Engineering Technology (IJRASET) Vol. 5(IX), 2017.

https://doi.org/10.22214/ijraset.2017.9076

[15] Rao N.G., Srikanth P.C., Sharan P., A novel quantum dot cellular automata for 4bit code converters. International Journal for Light and Electron Optics, 2016, 127 P. 4246–4249.

[16] Md. Tajul Islam, Golam Sarwar Jahan, Ali Newaz Bahar, Kawsar Ahmed, Md. Abdullah-Al-Shafi, A new efficient non-reversible 4 bit binary to gray and 4 bit gray to binary converter in QCA, Nanosystems: Physics, Chemistry, Mathematics, 2018, 9 (4), P. 473–483.

[17] Nandini G. Rao, P.C. Srikanth, and Preeta Sharan, A novel quantum dot cellular Automata for 4-bit code converters, Optik, Vol. 127, No. 10, pp. 4246–4249, 2016. https://doi.org/10.1016/j.ijleo.2015.12.119

[18] Ehsan Taher, Karkaj Saeed, and Rasouli Heikalabad, Binary to gray and gray to binary converter in quantum-dot cellular automata, Optik, Vol. 130, 2017, 981-989.

[19] Jadav Chandra Das, and Debashis De, Reversible Binary to Grey and Grey to Binary Code Converter using QCA, IETE Journal of Research, Vol. 61, No. 3, pp. 223-229, 2015.

[20] Siva Kumar M., Syed Shameem S., Raghu Sai M.N.V., Nikhil D., Kartheek P., Hari Kishore K, Efficient and low latency turbo encoder design using Verilog-Hdl, 2018, International Journal of Engineering and Technology(UAE), Vol: 7, Issue: 3.27 Special Issue 27, pp: 609 - 612.

https://doi.org/10.14419/ijet.v7i1.5.9119